三星公布64层NAND 芯片容量512Gb

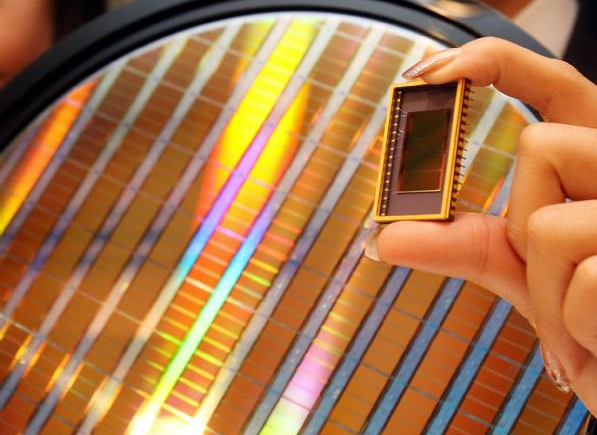

三星与东芝的64层3D NAND闪存技术,三星的CTF格式化检测技术,较受瞩目。图为三星的闪存。法新社

世界最大的尖端半导体相关技术国际学术会议,国际固态电路研讨会(ISSCC)的2017年度大会中,三星电子(Samsung Electronics),及美国威腾(Western Digital)与日本东芝(Toshiba)的合作团队,都公布了64层、512Gb容量的3D NAND闪存,且基本的读写速度与技术特征都相似。

据日本PC Watch网站的半导体业专家福田昭报导,虽然三星与东芝公布的产品类似,但发表后的反应却截然不同。对东芝方面只有1个工程师提出发问,三星方面则大排长龙,显示三星的技术有其特出之处,值得关注。

三星这次推出的64层3D NAND,被该厂归类于第三代技术,与第二代的48层相比,最大的技术障碍是垂直穿孔要穿透的层数增加3分之1,这要不是穿孔深度增加,就是每层之间的厚度要减薄,而厚度减薄可能减薄每层之间的绝缘层厚度,如何降低互相干涉导致数据存取发生错误,就是最主要的课题。

而三星特有的闪存制程技术,电荷撷取闪存(Charge Trap Flash;CTF),是以电荷撷取(Charge Trap)膜或电洞捕捉作为载子的电子,藉此记录或消去数据。

而这技术的主要问题,在于载子的能阶,能把载子固定在电荷撷取膜的深层缺陷区内,则载子便比较不易受到电流或温度的变化而逃脱,记忆比较容易保存,若载子仅被固定在浅层区,记忆便容易随载子的逃脱而消失,意味的就是内存性能劣化。

但是,当3D NAND闪存以减薄厚度的方式增加层数,则电荷撷取膜的厚度变薄,载子就比较容易被固定在浅层区,这意味着随3D NAND闪存层数增加,良率便将随之明显下跌,若不能克服这个问题,则3D NAND闪存便缺乏商用价值。

三星现在发展的技术,就是在初次记忆体格式化的过程中,顺便检查与消除浅层区,原则上是让内存的每个记忆单元,依其连接线路分成奇数组与偶数组,分别对奇数组与偶数组加高电压清除浅层区,经仔细调整,记忆单元不良率可降低为7%。

随智能型手机与个人计算机性能提升,大容量闪存芯片的需求跟着增加,现在新的512Gbit闪存芯片推出,可望更进一步提高记忆卡与SSD的性能,值得仔细观察。